### Number Systems

Tuesday, January 4, 2022 11:10 AM

Tuesday, January 4, 2022 11:57 AM

Basic Terminolog

"Voltage: Electric potential difference

Current: Flow of charged particles

$$\frac{\partial Q}{\partial t}$$

, always from (+) -> (-)

Ohm's Law: V= IR, in general V= IZ

CMOS Switch

Complimentary Metal Oxide Semiconductor: La Negative ; conducts when gate is 1 La Positive : conducts when gute is 0

closed, switch acts as a resistor when

conducts

does not conduct

gate

does not conduct

conducts

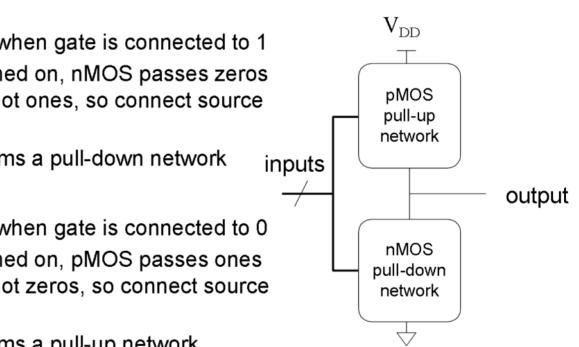

### nMOS, pMOS: Properties Summarized

Thursday, January 6, 2022 12:10 PM

- nMOS: •

- Turns on when gate is connected to 1

- When turned on, nMOS passes zeros well, but not ones, so connect source to GND

- nMOS forms a pull-down network

- pMOS: ٠

- Turns on when gate is connected to 0

- When turned on, pMOS passes ones well, but not zeros, so connect source to  $V_{DD}$

- pMOS forms a pull-up network

#### Logic Gates, Boolean Algebra Axioms and Theorems

Thursday, January 6, 2022 11:02 AM

Axioms and Theorems

|    | Axiom                           |     | Dual                  | Name         |

|----|---------------------------------|-----|-----------------------|--------------|

| A1 | $B = 0$ if $B \neq 1$           | A1' | $B = 1$ if $B \neq 0$ | Binary field |

| A2 | $\overline{0} = 1$              | A2′ | $\overline{T} = 0$    | NOT          |

| A3 | $0 \bullet 0 = 0$               | A3′ | 1 + 1 = 1             | AND/OR       |

| A4 | $1 \bullet 1 = 1$               | A4′ | 0 + 0 = 0             | AND/OR       |

| A5 | $0 \bullet 1 = 1 \bullet 0 = 0$ | A5′ | 1 + 0 = 0 + 1 = 1     | AND/OR       |

|    | Theorem                      |                               | Dual                   | Name         |

|----|------------------------------|-------------------------------|------------------------|--------------|

| T1 | $B \bullet 1 = B$            | T1′                           | B + 0 = B              | Identity     |

| T2 | $B \bullet 0 = 0$            | T2′                           | B + 1 = 1              | Null Element |

| T3 | $B \bullet B = B$            | T3′                           | B + B = B              | Idempotency  |

| T4 |                              | $\overline{\overline{B}} = B$ |                        | Involution   |

| T5 | $B \bullet \overline{B} = 0$ | T5′                           | $B + \overline{B} = 1$ | Complements  |

|            | Theorem                                                                                                                                     |      | Dual                                                                                                                | Name                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------|------------------------|

| T6         | $B \bullet C = C \bullet B$                                                                                                                 | T6'  | B + C = C + B                                                                                                       | Commutativity          |

| <b>T</b> 7 | $(B \bullet C) \bullet D = B \bullet (C \bullet D)$                                                                                         | T7'  | (B+C)+D=B+(C+D)                                                                                                     | Associativity          |

| T8         | $(B \bullet C) + B \bullet D = B \bullet (C + D)$                                                                                           | T8′  | $(B+C)\bullet(B+D)=B+(C\bullet D)$                                                                                  | Distributivity         |

| T9         | $B \bullet (B + C) = B$                                                                                                                     | T9′  | $B + (B \bullet C) = B$                                                                                             | Covering               |

| T10        | $(B \bullet C) + (B \bullet \overline{C}) = B$                                                                                              | T10' | $(B+C)\bullet(B+\overline{C})=B$                                                                                    | Combining              |

| T11        | $ \begin{aligned} (B \bullet C) + (\overline{B} \bullet D) + (C \bullet D) \\ = B \bullet C + \overline{B} \bullet D \end{aligned} $        | T11′ | $ \begin{aligned} (B+C) \bullet (\overline{B}+D) \bullet (C+D) \\ &= (B+C) \bullet (\overline{B}+D) \end{aligned} $ | Consensus              |

| T12        | $ \begin{array}{c} \overline{B_0 \bullet B_1 \bullet B_2 \dots} \\ = (\overline{B_0} + \overline{B_1} + \overline{B_2} \dots) \end{array} $ | T12' |                                                                                                                     | De Morgan's<br>Theorem |

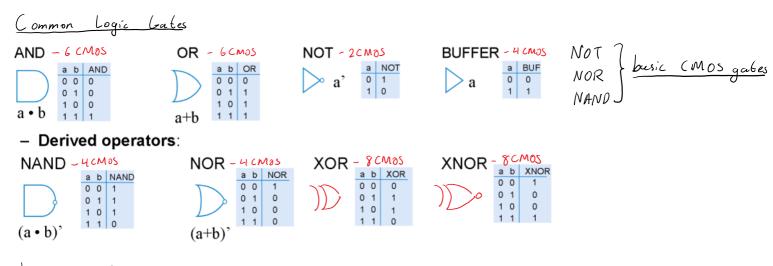

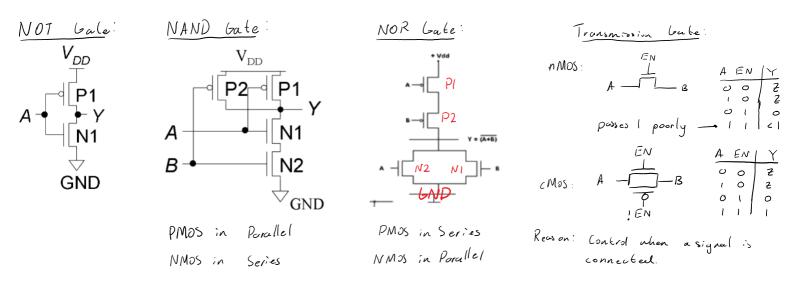

Logic Gates From CMOS, Delay

Thursday, January 6, 2022 12:11 PM

<u>Delay</u>! Delay is linear to resistance - capacitence. Loing through a transistor has resistance and input into a transistor gate has capacitence. For multiple stages, delay is addrtive

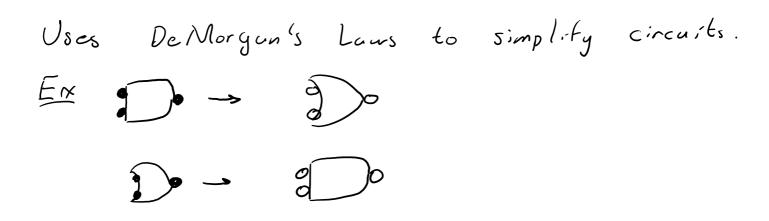

# **Bubble Pushing**

Thursday, January 6, 2022 12:00 PM

1) Convert AND La OR

- 2) Convert < 0

- 3) combine o until simplified.

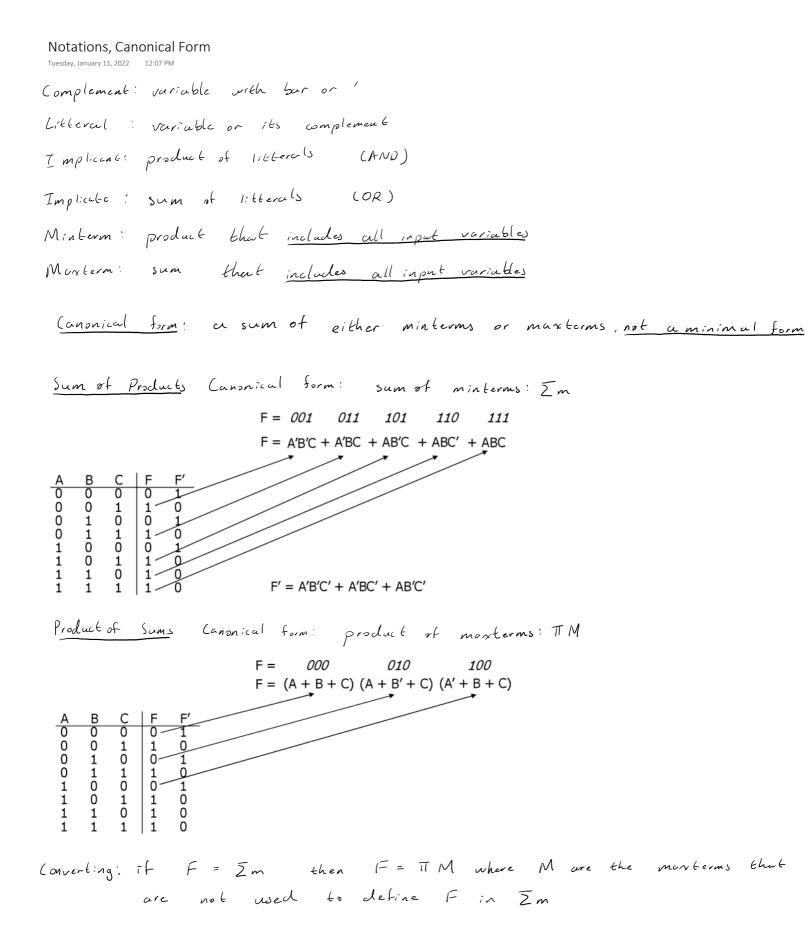

#### Terms for 2-Level Simplification, Kmap Simplification

Tuesday, January 18, 2022 11:26 AM

Implicant : Any observed of ON-set or DC-set, Implicate: Any element of OFF-set or DC-set

Prime: largest group of implicats/implicates that are powers of

Essential Prime: a Prime that alone covers on element of ON-set

Def Algorithm:

Find Prime Emplicants

Filter only the Essential Prime Implicants to minimize size and terms

Create onisterms or maxterns according to the Prime Implicants

Note Don't cores can form primes but not essential primes.

Specifically: If a don't care can be used to form a larger group with another implicate, then it is included in a prime.

A don't core by itself will not form a prime.

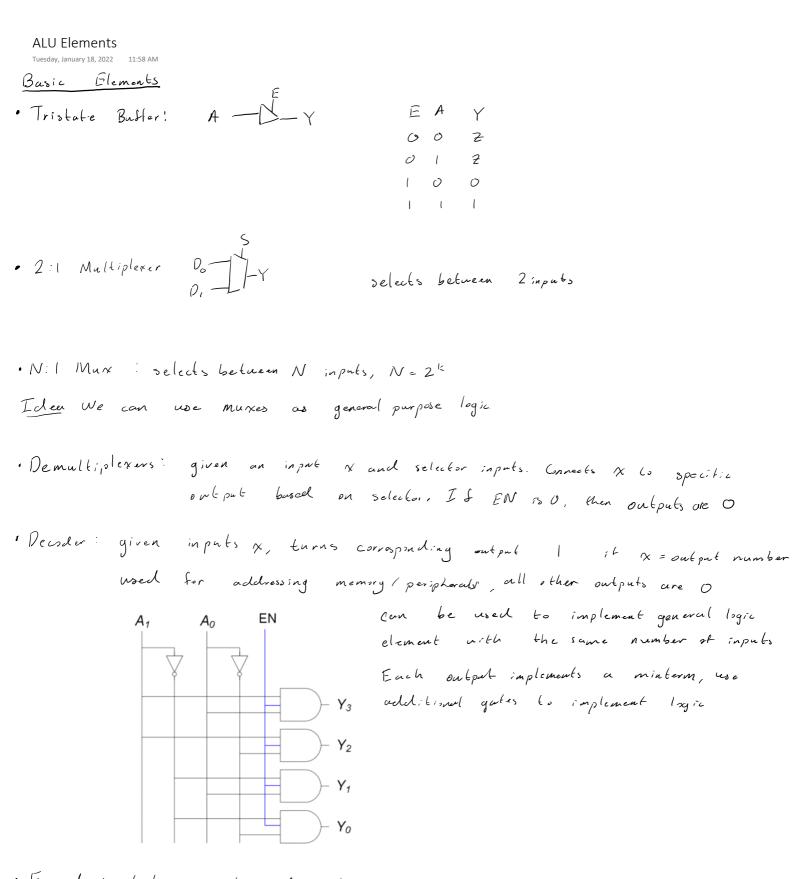

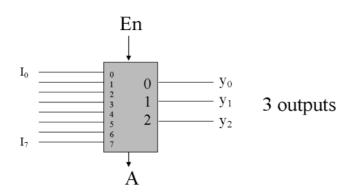

· Encoder: takes inputs and sets corresponding output to 1, else 0:

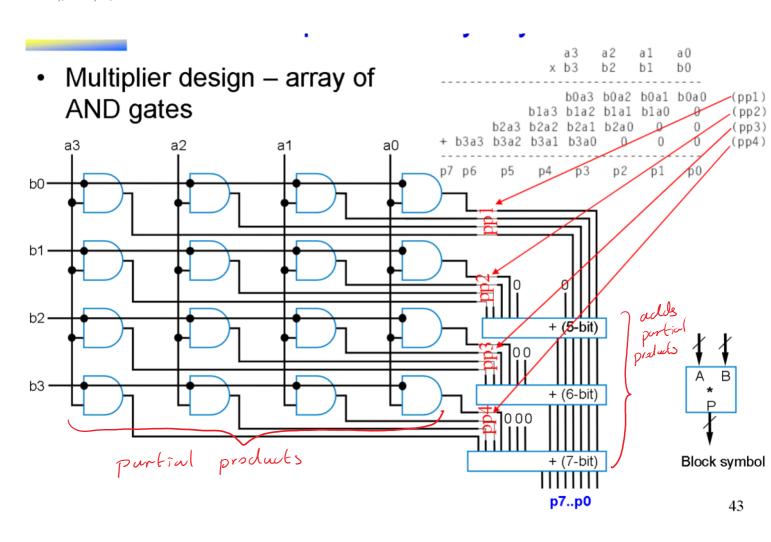

### Basic Processor Design

Saturday, January 22, 2022 2:22 PM

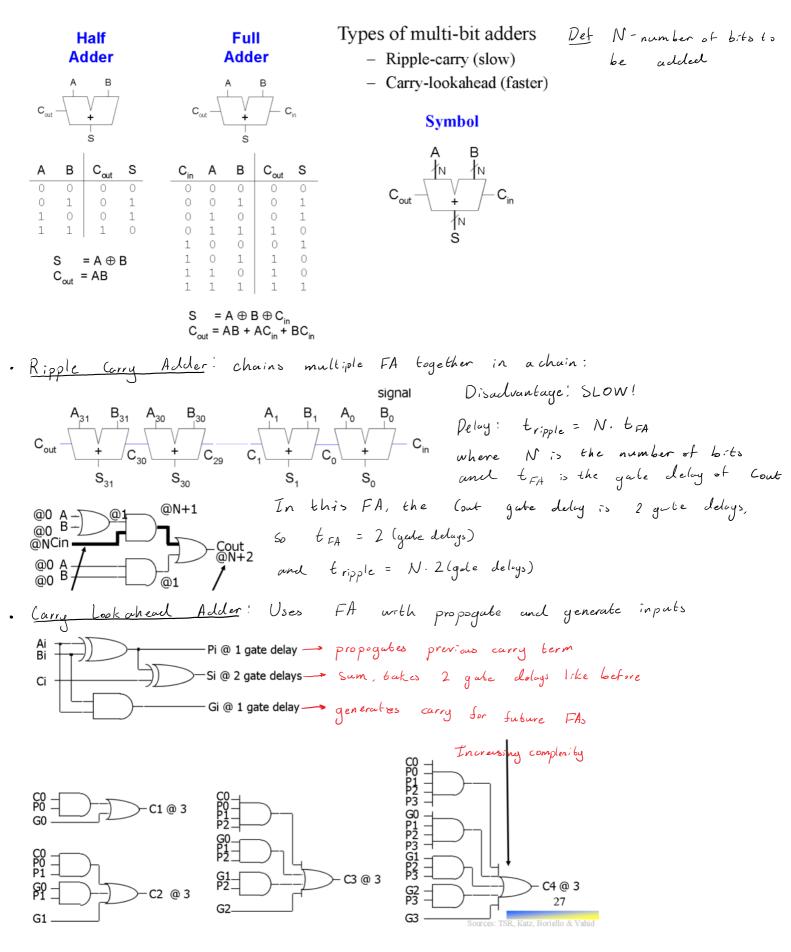

Disadvantage ! increasing complexity as Nincreases

#### Generally:

- Step 1: Compute  $G_i$  and  $P_i$  for all columns

- Step 2: Compute G and P for k-bit blocks

- Step 3: C<sub>in</sub> propagates through each k-bit propagate/generate block

$G_{i:j} = G_i + P_i (G_{i-1} + P_{i-1} (G_{i-2} + P_{i-2}G_j))$  $\boldsymbol{P}_{i:j} = \boldsymbol{P}_i \boldsymbol{P}_{i-1} \, \boldsymbol{P}_{i-2} \boldsymbol{P}_j$  $\sim$  $C_i = G_{i:j} + P_{i:j}C_{i-1}$

Iden: We can combine ripple curry and carry lookahead adders to create a fast and smell adder.

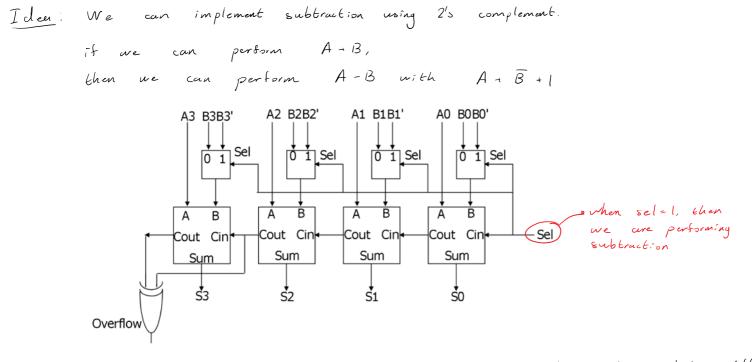

Subtractor (2's Complement)

Saturday, January 22, 2022 2:48 PM

Delecting overflow: 1) It the two input sign bits are the same but result sign bit is different 2) Difference between cin of sign bit and cout of sign bit to simpler logic using I war gate.

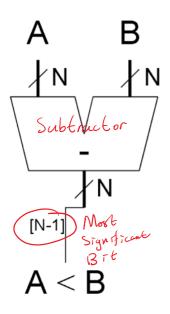

### Comparators (Equal, Less Than, Greater Than)

Saturday, January 22, 2022 3:01 PM

Equality (omparator) Symbol Implementation Equal is only true when A = B  $A_3 = D$   $A_4 = A_4$   $A_2 = D$   $A_2 = D$   $B_2 = D$   $B_1 = D$  $B_0 = D$

Less Than / Greater Than:

| When | output | íð | Ι, | then | A < B |

|------|--------|----|----|------|-------|

| when | output | 5  | 0, | then | AZB   |

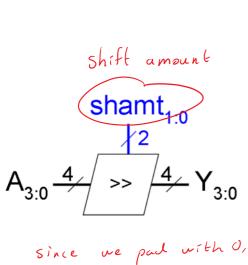

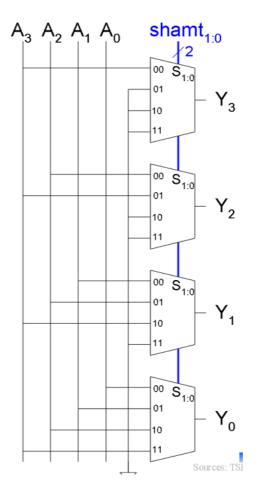

Shifters (Logical, Arithmetic, Rotator)

Saturday, January 22, 2022 3:05 PM

Logical Shifter: Fill empty spaces with O Arithmetic Shifter: On right shift, fill empty spaces with old MSB Rotator: Wrap bits shifted off the end to new empty space

Ehris is a Logical Shitter.

# Repeated subtraction

### Example: • Dividend: 101; Divisor: 10

- Set quotient to 0

Repeat while dividend >= divisor

Subtract divisor from dividend

Add 1 to quotient

- When dividend < divisor:</p>

- Reminder = dividend

- Quotient is correct

Dividend

Quotient

101

0

+

10

1

1

11

1

+

10

1

+

11

1

+

10

1

1

10

1

10

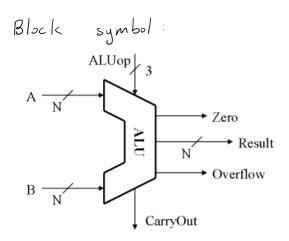

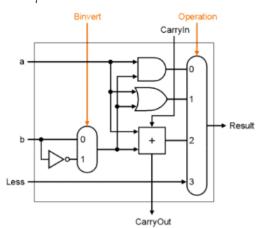

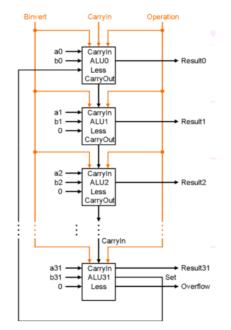

#### ALU Design

Saturday, January 22, 2022 3:12 PM

| ALU Control Lines (ALUop) | Function         |

|---------------------------|------------------|

| - 000                     | And              |

| - 001                     | Or               |

| - 010                     | Add              |

| - 110                     | Subtract         |

| - 111                     | Set-on-less-than |

I dea! We can chain together multiple 1-bit ALUS together to create larger ALUS capuble of larger number operations.

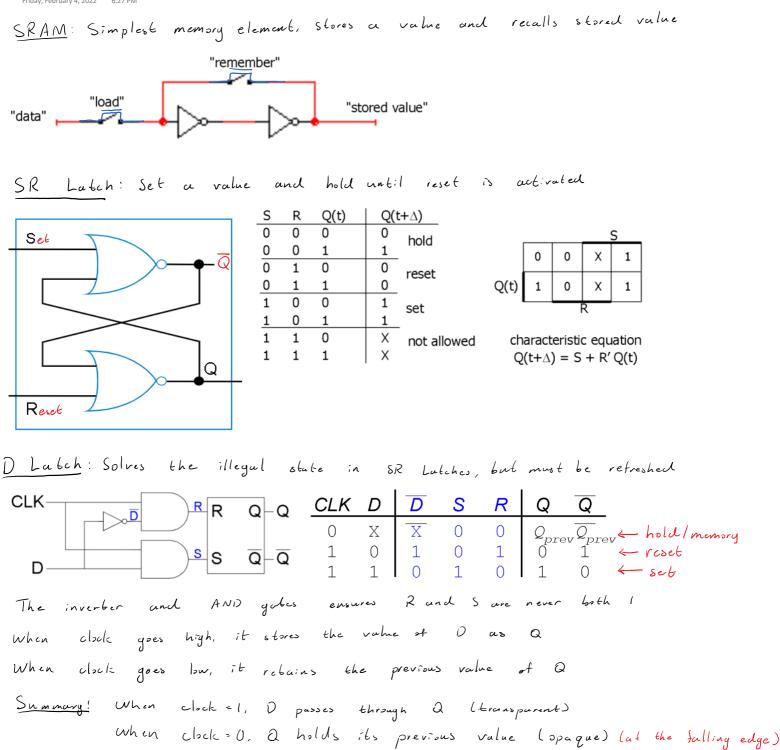

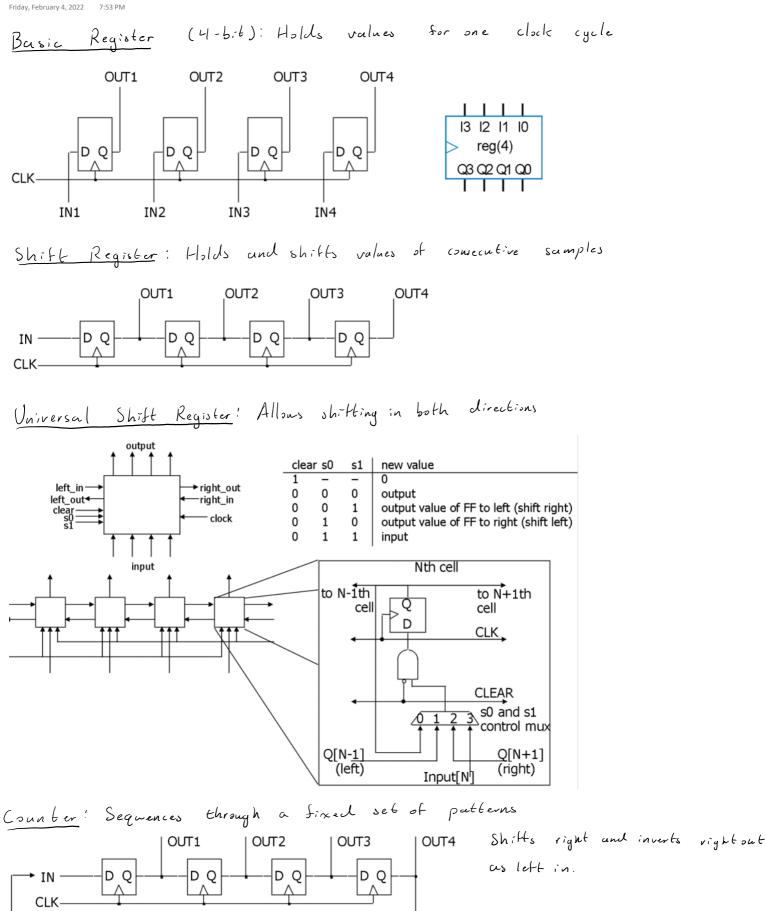

Sequential Logic Components

Friday, February 4, 2022 6:00 PM

Idea: We want to create circuits to store data so that we can run a sequence of tasks.

SRAM, SR Latch, D Latch

Friday, February 4, 2022 6:27 PM

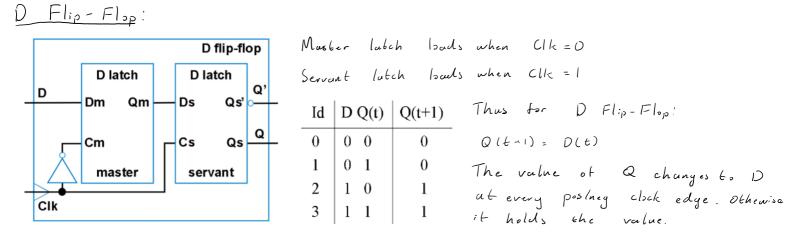

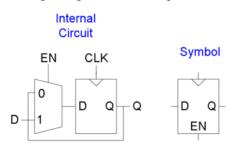

#### D Flip-Flop

Friday, February 4, 2022 7:06 PM

Adding an Enable:

-EN = 1: D passes through to Q on the clock edge

- **E**N = **0**: the flip-flop retains its previous state

Friday, February 4, 2022 7:42 PM

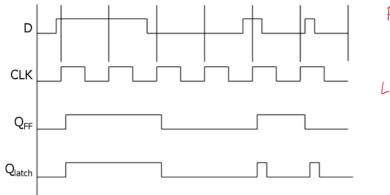

Latch! Copies D when CLK=1, holds previous value when CLK=0. Basic Register, Shift Register, Counter

Friday, February 4, 2022 8:08 PM

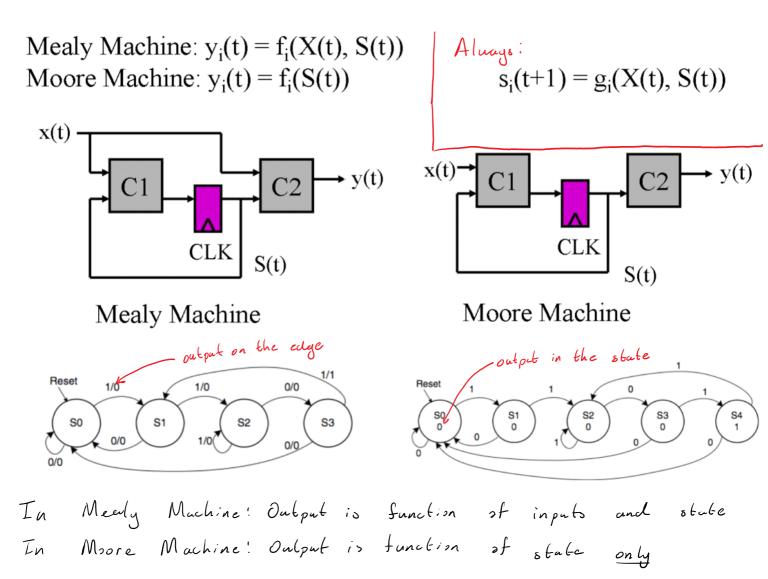

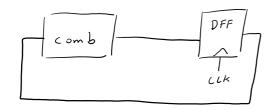

In combinational logic, we had no feedback. Idra! In sequential logic, we have teadback and memory, which we can make Sinite state machines. Det An FSM consists of: - set of states - set of inputs and outputs - initial state - set of transitions, only one can be true at a time Notation: State Diagram: Graph where nodes are states and directed edges are transitions Stute Table: Table showing each current state and next states State Assignments: Binary representation of each state Excitation Table: State Table but with state Assignments Creating A Circuit: Excitation Table shows the combinational logic: Comb output where NS is the next state CS is the current state Registers are D Flip-Flop(s) Combinational NS Registers

Finding combinational: Use k-maps where each output next stale are outputs and inputs/current stale are inputs.

Friday, February 4, 2022 8:34 PM

FSM Timing Sunday, February 13, 2022 1:30 PM

Det: For combinational logic!

Min delay of a gate, also called contamination delay:  $t_{cd}$ Minimum time from when an input changes until the output starts to change Max delay of a gate, also called propagation delay:  $t_{pd}$

Maximum time from when an input changes until the output is guaranteed to reach its final value (i.e., stop changing)

On inputs' Setup time: t<sub>setup</sub>

Time *before* the clock edge that data must be stable (i.e. not change) Hold time:  $t_{hold}$ Time after the clock edge that data must be stable Aperture time:  $t_a$ Time around clock edge that data must be stable  $(t_a = t_{setup} + t_{hold})$

On ontputo: Min delay of FF, also called contamination delay or min CLK to Q delay:  $t_{ccq}$ Time after clock edge that Q might be unstable (i.e., starts changing) Max delay of FF, also called propagation delay or maximum CLK to Q delay:  $t_{pcq}$ Time after clock edge that the output Q is guaranteed to be stable (i.e. stops changing)

Det: For clock signal!

The clock doesn't arrive at all registers at the same time **Skew:** difference between the two clock edges Perform the **worst case analysis**

### High Level State Machine

Sunday, February 13, 2022 2:35 PM

Conventions - Numbers:

- Single-bit: '0' (single quotes)

- Integer: 0 (no quotes)

- Multi-bit: "0000" (double quotes)

- == for comparison equal

- Multi-bit outputs *must* be registered via local storage

- // precedes a comment

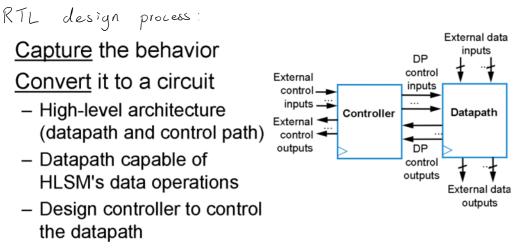

RTL Design Sunday, February 13, 2022 2:52 PM

# Steps: 1) Draw the HLSM 2) Determine what data will be stored and how it will be modified. L Design the Datapath (Sequential Circuit) 3) Determine how to control the Datapath, what states have what control signals Lo Design the Controller (FSM)

- Det: A Data dominant design: extensive datapath, simple controller

- A Controll dominant design: simple datapath, extensive controller

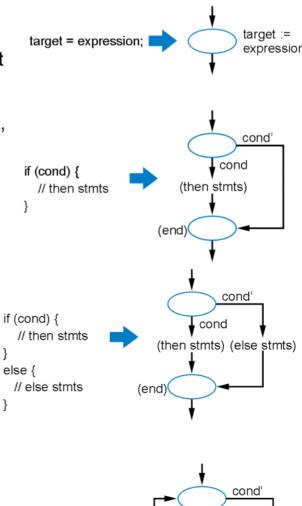

# Assignment statement

- Becomes one state with assignment

# If-then statement

- Becomes state with condition check, transitioning to "then" statements if condition true, otherwise to ending state

- "then" statements would also be converted to states

## lf-then-else

Becomes state with condition check, transitioning to "then" statements if condition true, or to "else" statements if condition false

# While loop statement

Becomes state with condition check, transitioning to while loop's statements if true, then transitioning back to condition check

while (cond) {

}

// while stmts

cond

(while stmts)

(end)

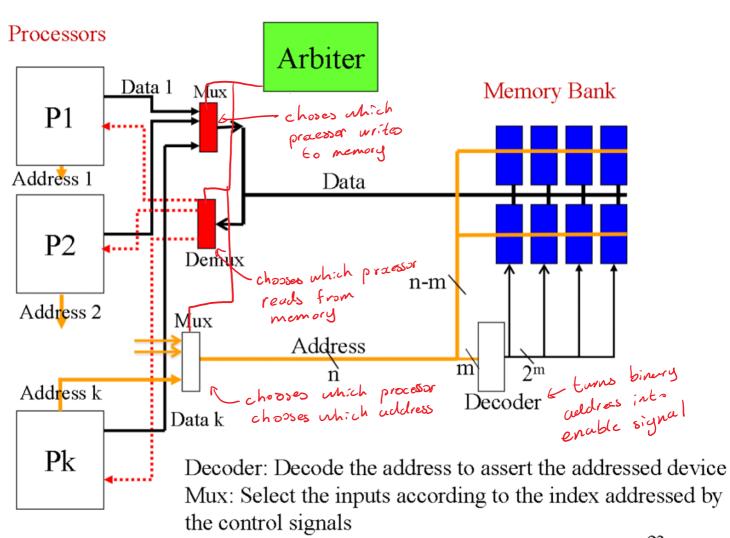

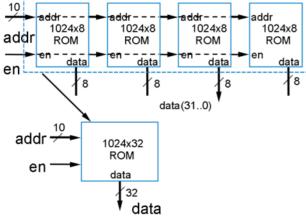

Memory, RAM vs ROM

Saturday, February 26, 2022 4:23 PM

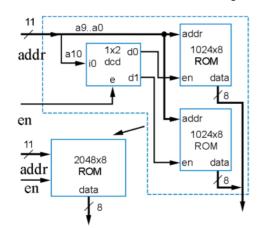

Combining! More memory: connect memory in parallel with decoder:

Det Traditionally: ROM is read-only, bits stored without power RAM is dynamic, bits lost without power

Lotely, distinctions blurred: Advanced ROMs can be written to (EEPROM) Advanced RAMs can hold bits without power (NVRAM)

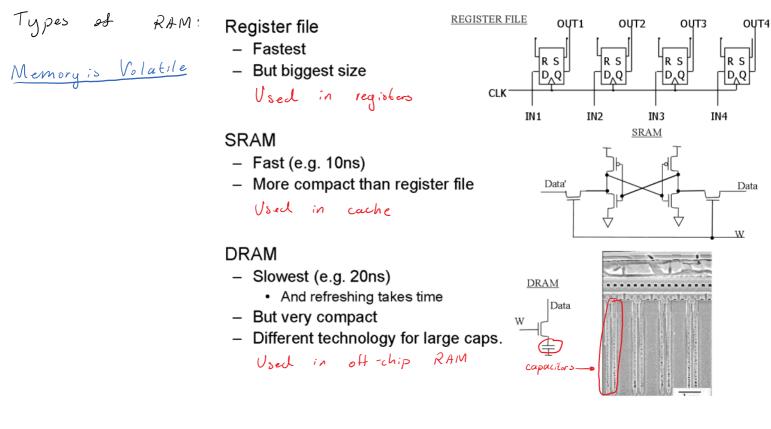

RAM, Types of RAM Saturday, February 26, 2022 4:44 PM

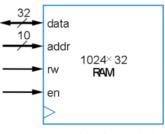

Det Block symbol and characteristics st RAM

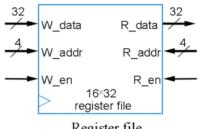

### RAM – Readable and writable memory

- Logically the same as register file

- RAM just one port; register file two or more

- RAM vs. register file

- RAM is larger

- RAM stores bits using a bit storage vs. FFs

- RAM implemented on a chip in a square keeps longest wires (hence delay) short

RAM block symbol

Saturday, March 5, 2022 12:40 PM

Idea: We want to store data without having to retresh the bits We can use ROMs

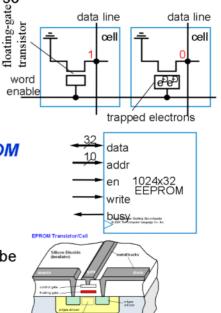

Det: Traditional ROMS use quantum tanneling to trap data in a Sloating gate. Use a strong voltage to free electron.

### Erasable Programmable ROM (EPROM)

- Uses "floating-gate transistor" in each cell

- Programmer uses higher-than-normal voltage so electrons *tunnel* into the gate

- Electrons become trapped in the gate

- Only done for cells that should store 0

- · Other cells will be 1

- To erase, shine ultraviolet light onto chip

- · Gives trapped electrons energy to escape

- · Requires chip package to have window

# Electronically-Erasable Programmable ROM (EEPROM)

- Programming similar to EPROM

- Erasing one word at a time *electronically*

#### Flash memory

Like EEPROM, but large blocks of words can be erased simultaneously

# EEPROM & FLASH are in-system programmable

hid, Perkowski

#### Modern/New Memory Types

Saturday, March 5, 2022 12:46 PM

FERAM: stores data in ferroelectric material. No refresh, similar performance to DRAM but destructive reads

- STT-RAM: Stores data in tunneled electrons. Value determined by electron spin. High endurance, fast reads but high write energy

- PCM! Stores data by changing state of material using a heater. bood scalability but slow writes, low endurance.

- ReRAM: Stores duta by changing the resistance of a semiconductor. Fast read/write, high density but limited endurance

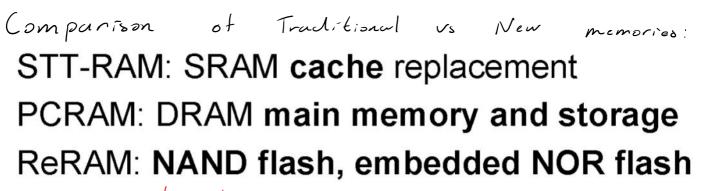

### Comparison of New vs Traditional Memories

Saturday, March 5, 2022 12:58 PM

|                  | La als    | ilso for near-memory compute |                                         |                                          |                                       |

|------------------|-----------|------------------------------|-----------------------------------------|------------------------------------------|---------------------------------------|

| Features         | SRAM      | eDRAM                        | STT-RAM                                 | PCRAM                                    | ReRAM                                 |

| Density          | Low       | High                         | High                                    | Very high                                | Very high                             |

| Speed            | Very Fast | Fast                         | Fast for read;<br>slow for write        | Slow for<br>read; very<br>slow for write | Slow for read/write                   |

| Dynamic<br>Power | Low       | Medium                       | Low for read;<br>very high for<br>write | Medium for<br>read; high for<br>write    | Medium for<br>read; high for<br>write |

| Leakage<br>Power | High      | Medium                       | Low                                     | Low                                      | Low                                   |

| Non-volatility   | No        | No                           | Yes                                     | Yes                                      | Yes                                   |